- 16 高校采購信息

- 179 科技成果項目

- 1 創新創業項目

- 0 高校項目需求

ZL-MOVE 卷積神經網絡處理器及其開發系統

為了能夠使基于卷積神經網絡的深度學習技術得以更廣泛的應用,需要盡可能地降低其應用系統的設計與開發成本,并使其體積和功耗降至最低。本團隊開發設計了一種稱之為ZL-MOVE的新型卷積神經網絡處理器(NPU)體系架構,該架構基于控制數據傳輸并觸發相關操作的簡潔指令及規則的二維陣列并行計算結構,可以非常便捷的實現電路的參量化設計及簡單易用的應用程序編譯器設計,從而可以達到針對具體應用進行處理器硬件電路和軟件編譯器定制化設計的目的,從而使系統電路和應用程序設計簡單、高效,能夠方便地應用于諸如智能傳感器和物聯網IoT等對體積、重量及功耗要求嚴格的嵌入式應用領域。

團隊設計的ZL-MOVE神經網絡處理器采用了將傳輸觸發體系結構TTA 與復雜指令集體系結構CISC相結合的新型的適于邊緣計算的并行計算機體系結構,其指令的功能與機器代碼格式與TTA指令一致,保持了TTA指令所具備的指令與數據并行操作的特點,而其指令的執行又具有CISC結構多周期執行的特點,非常適用于數據傳輸與計算密集型的應用。在實際的應用中,ZL-MOVE體系結構的NPU既可以開發程序中指令的并行性,又可以開發數據的并行性,同時指令的多周期執行方式完善了指令的功能和執行效率,并且可以極大地提高處理器的最高工作頻率。

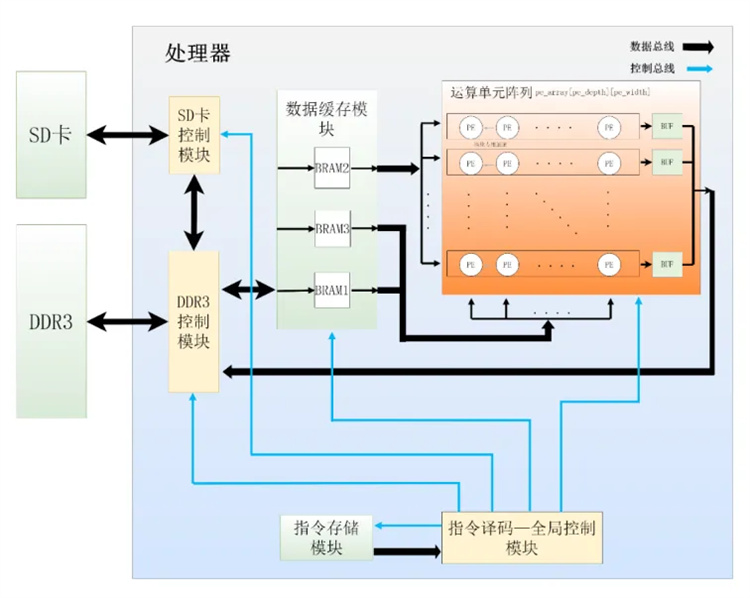

下圖是ZL-MOVE架構卷積神經網絡處理器的結構框圖。其設計的核心思路是采用數據傳輸MOVE指令以DMA數據塊傳輸方式將一組運算數據傳送到高速數據緩沖區中,再根據指令中給出的操作目的地址觸發相應的多周期操作來實現卷積神經網絡中的卷積、池化、殘差、非線性函數和全連接等運算操作,而這些操作均通過參數可配置硬件狀態機和以2維方式構建的大規模并行處理單元(PE)陣列加以實現。

圖 1 ZL-MOVE 神經網絡處理器結構圖

由于ZL-MOVE體系架構NPU的指令功能極為簡單,即通過將運算操作數傳輸至指定的處理單元,并觸發該單元完成相應的處理操作,因而可以非常方便的為其設計應用程序編譯器以及包括軟件虛擬機和系統調試器在內的系統軟硬件綜合開發調試工具,從而可以大幅降低應用程序的開發和調試難度,提高系統的設計效率。

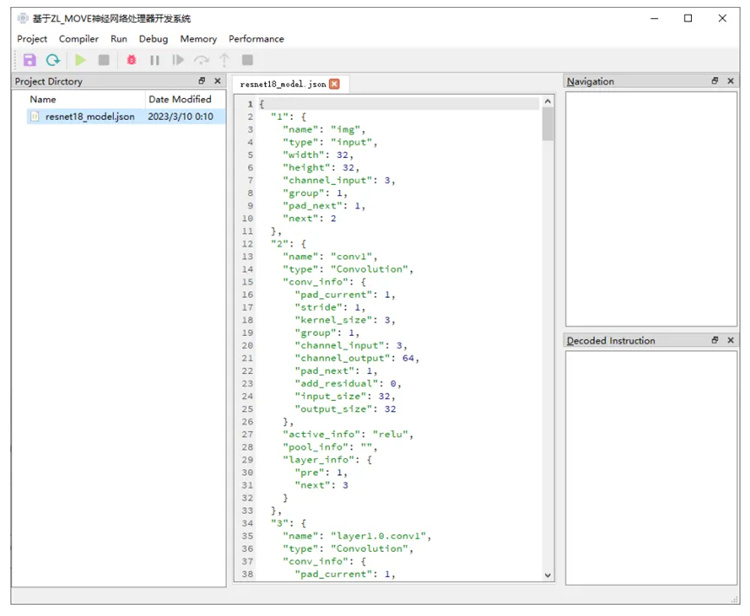

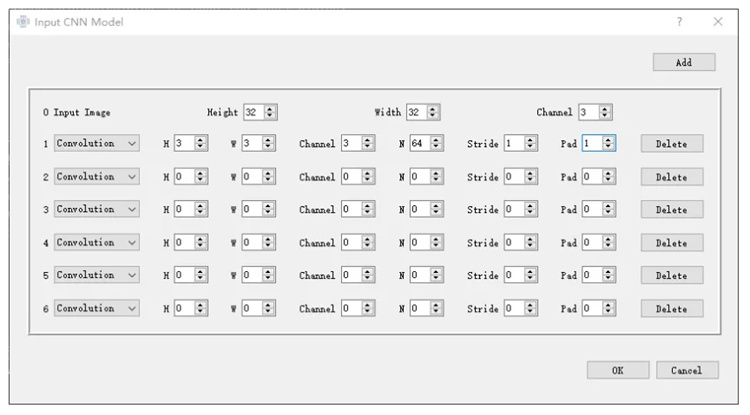

下圖是是ZL-MOVE神經網絡處理器軟硬件綜合開發系統的圖形化界面,圖(a)是軟硬件綜合開發系統主界面,圖(b)是應用程序編譯器中卷積神經網絡CNN模型參數定義界面,用戶通過圖形化或JSON格式的CNN結構及參數描述文件即可以輸入將要編程實現的CNN模型及其相關參數,編譯器據此就可以自動生成完成該網絡前向推理運算所需的全部應用程序指令。

(a)軟硬件綜合開發系統主界面

(b)應用程序編譯器 CNN 網絡結構定義界面

圖 2 ZL-MOVE 神經網絡處理器軟硬件開發系統圖

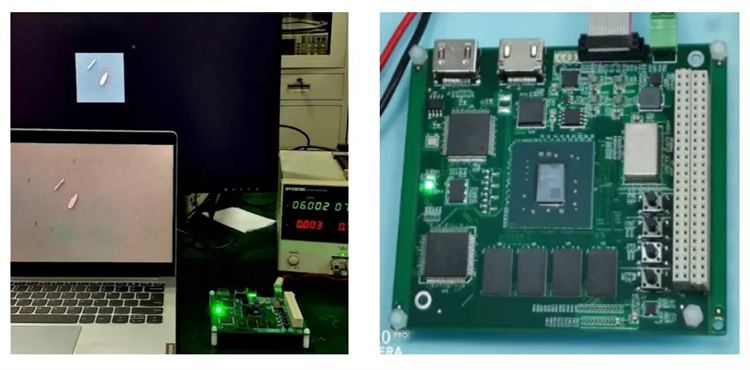

課題組設計的ZL-MOVE神經網絡處理器及其軟硬件開發系統已經成功的應用于實際的工程項目中,下圖所示是基于上述系統實現的基于模板的深度學習目標檢測定位系統實物圖,該系統采用Xilinx Kintex-7 XC7K410T FPGA實現,NPU中并行處理單元(PE)數量為1024,可以實現256*256 圖幅檢測區域的基于模板(圖幅32*32)的目標檢測和定位,速度可達400幀/秒,當IoU為50%時,檢測準確率可達85%以上。系統PCB尺寸為90*96*10mm,重量為78克,系統功耗為4.4W。

圖 3 基于 ZL-MOVE 神經網絡處理器的應用系統實物圖

原理樣機

掃碼關注,查看更多科技成果