- 74 高校采購信息

- 3295 科技成果項目

- 0 創新創業項目

- 0 高校項目需求

智能機器人視覺識別芯片

在信息時代,機器視覺在實現智能社會方面發揮著重要作用。視覺特征提取是機器視覺的一項關鍵技術,該技術可以提取圖像中具有鮮明特征的信息,諸如邊緣、角點、圓以及圖像形狀等特征,這些特征是標定機器視覺系統模型參數和運用機器視覺技術進行實際應用的前提和基礎。視覺特征提取技術廣泛應用于自主移動智能機器人、無人駕駛和無人機等場景,這些應用場景對視覺特征提取算法的魯棒性和幀率提出了巨大挑戰。

具體來說,視覺特征提取算法包括SIFT(Scale-Invariant Feature Transform,尺度不變特征轉換算法)、SURF(Speeded-Up Robust Features,加速穩健特征)、ORB(Oriented FAST and Rotated BRIEF,快速特征點提取描述)、HOG(Histogram of Oriented Gradient,方向梯度直方圖)、LBP(Local Binary Patterns,局部二值模式)等。在SURF、ORB、HOG、LBP這些經典的特征提取算法中,SURF的魯棒性相對較高,但是過于依賴主方向的選取,使得其方向變化魯棒性不足。SIFT算法可以從圖像中提取具有不變性的魯棒局部特征,對方向變化、光照變化、噪聲、雜物場景及遮擋影響等方面的魯棒性最強,滿足無人駕駛技術的需求。SIFT算法的運算量大從而導致的系統幀率低、功耗高的問題可以通過設計具有高并行度的專用硬件加速器芯片來解決。

視覺特征提取技術廣泛應用于自主移動智能機器人、無人駕駛和無人機等場景。

基于其初步研究成果,團隊已與黑芝麻科技等自動駕駛頭部企業合作,聯合承擔了武漢市科技重大專項“卡脖子”技術攻關項目,研究高魯棒性、高能效視覺目標識別引擎電路技術,進行車規級高性能自動駕駛芯片設計關鍵技術的科技攻關。

國內外已有多個SIFT硬件加速器設計發表,總體的研究方向朝著更高性能、更高幀率、更高匹配精度以及更低功耗、更低運算量、更低硬件開銷的方向發展。但是對于高性能SIFT硬件加速器的設計仍存在如下三個共性問題和設計挑戰:

1.SIFT運算量大,需全并行、全流水架構進行加速,但并行高斯金字塔構建帶來了大量的硬件開銷;

2.高斯金字塔構建中部分特征點的丟失,使得加速器提取的特征魯棒性變差;

3.關鍵點檢測部分和描述符生成部分的內部串行執行,兩個部分交互執行的方式使得加速器處理速度存在瓶頸,造成系統幀率受限。

圖1 高性能SIFT硬件加速器的設計存在的三個共性問題和設計挑戰

【解決方案】

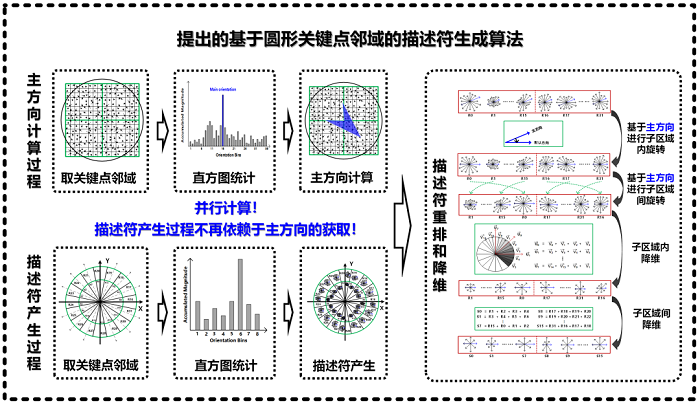

針對上述問題,本成果提出了一系列新方法和新策略,實現了全并行的高能效SIFT硬件加速器芯片硬件架構。針對高斯金字塔構建硬件開銷大的問題,提出了快慢雙時鐘域和部分復用策略;針對高斯金字塔構建過程中的特點丟失問題,提出了動態padding設計策略;針對交互執行及串行計算限制加速性能的問題,提出了一系列并行化的設計方案,即基于乒乓緩存實現了關鍵點檢測和描述符生成部分的并行處理,基于像素梯度預計算實現了關鍵點檢測和梯度幅值輔角的并行計算、以及創新性地提出了一種基于圓形關鍵點鄰域的描述符生成算法,實現了主方向和描述符產生的高效并行計算。

圖2 高性能SIFT硬件加速器的設計存在的三個共性問題和對應的設計策略及設計實現

圖3 提出的基于圓形關鍵點鄰域的描述符生成算法,可以實現主方向計算和描述符產生過程的并行化計算

【性能指標】

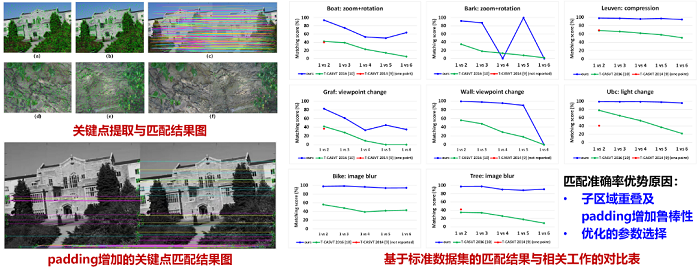

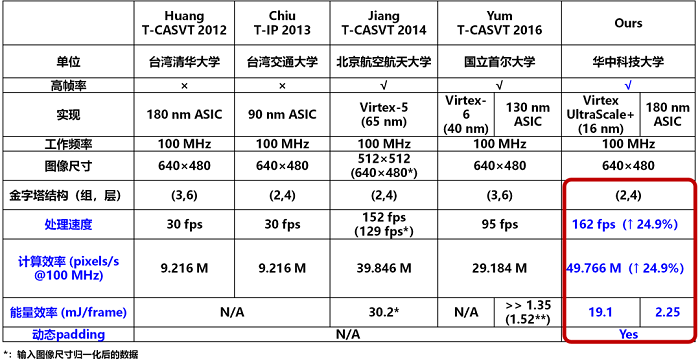

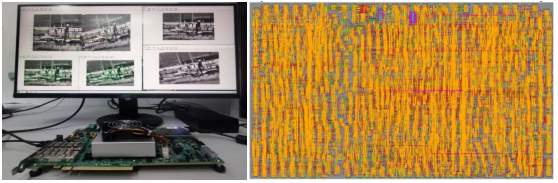

本成果研發的全并行高能效SIFT硬件加速器芯片已在Xilinx Virtex UltraScale+評估板中實現。基于Mikolajczyk and Schmid標準數據集對提出的SIFT設計進行驗證,基于RANSAC(RANdom SAmple Consensus)算法檢查匹配點的正確性。所提SIFT設計的匹配結果優于相關工作,這主要得益于子區域重疊及padding增加魯棒性,及優化的參數選擇(如高斯卷積核尺寸、關鍵點鄰域大小等)。與文獻中相關FPGA及ASIC工作的硬件開銷對比顯示:該設計的硬件開銷總體和現有水平相當,但通過實現了動態padding提高了魯棒性,同時實現了100 MHz時鐘下162 fps VGA的最高幀率和49.766 M pixels/s的最高計算效率。該SIFT硬件加速器在基于180 nm CMOS工藝下實現了2.25 mJ/frame的能量效率。

圖4 基于所提SIFT算法的關鍵點提取與匹配結果圖,基于標準數據集的匹配結果與相關工作的比較圖

圖5 SIFT硬件加速器處理性能比較表:該設計取得了國際SIFT硬件加速器芯片設計中最高幀率的學術記錄、最高計算效率和能量效率,并采用了動態padding技術提高了魯棒性

圖6 基于所提出的全并行高能效SIFT硬件加速器芯片的SoC驗證平臺及65nm芯片版圖

掃碼關注,查看更多科技成果